ISEの使い方

■ 全般

ザイリンクスから CLPD/FPGA開発;の統合開発環境としてISE(Integrated Software Environment) WebPACKが提供されています。無償版はザイリンクスのホームページからダウンロードで

きますが デバイスの種類、ゲート規模等に制限があります。

■ プロジェクトの作成(以下のPC画面画像は CPLD、FPGAが混在していたり、またいくつかのプロジェクト画面が混在しており、1つの一貫したプロジェクトの画像ではありません)

・ ISE(Project Navigater Ver 13.1) を起動させて、左上のプロジェクトウィンドウのStartタグを選択して下記のウィンドウを表示させます。

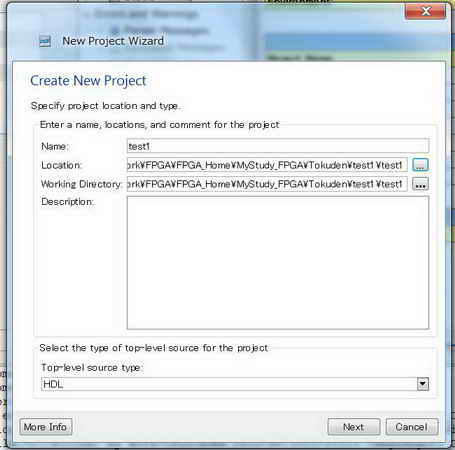

・NewProject のボタンをクリックすると下記のようなCreate New Projectのダイアログがあれわれるので、プロジェクト名、プロジェクトファイルのロケーション等を設定します。

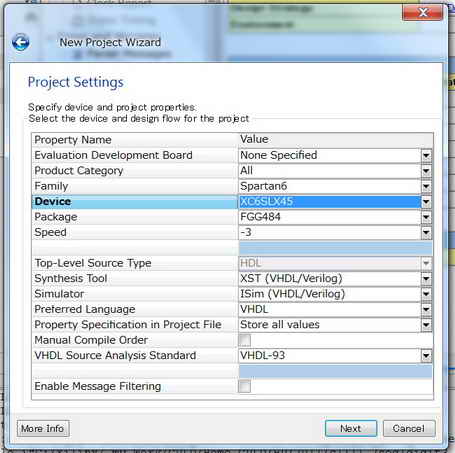

・Nextのボタンをクリックすると Project Settingのダイアログが現れるので Family, Device, Package,

Speed(通常-2 or -3 を選択),Preterred Language(VHDL or Verilog) 等を選択します。

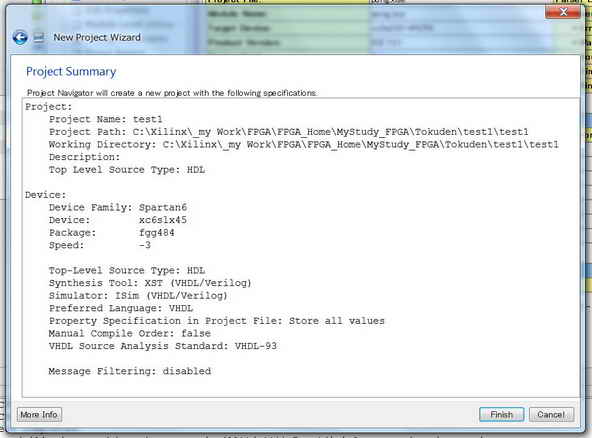

・Nextのボタンをクリックすると プロジェクトの内容確認の画面があらわれます。 確認したらFinishボタンをクリックします。

■ ソースフィルの作成

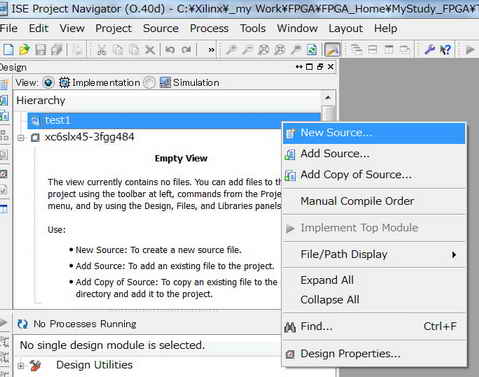

・プロジェクトエクスプローラ(仮称)のプロジェクト名(test1)を右クリックして ショートカットメニューを表示させます。

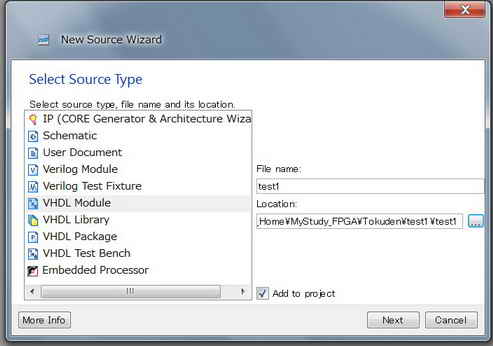

・ ダイアログがあれわせますので ソースファイルの種類(VHDLであればVHDL Module)を選択して ソースファイルの名前(通常プロジェクトの名前)を記載してNextをクリックします。

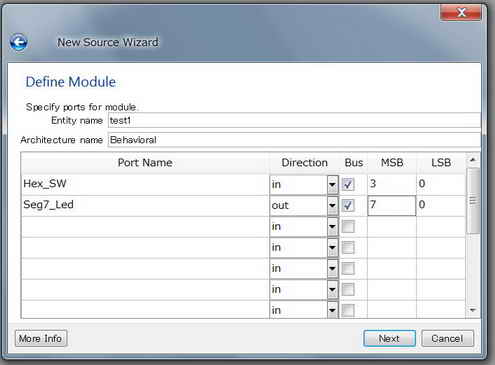

・ モジュールの入出力ポートの名称、数量について定義します。

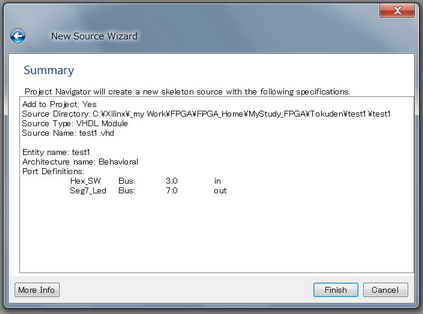

・ Nextボタンをクリックすると確認画面があらわれますのでよければFinishボタンをクリックします。

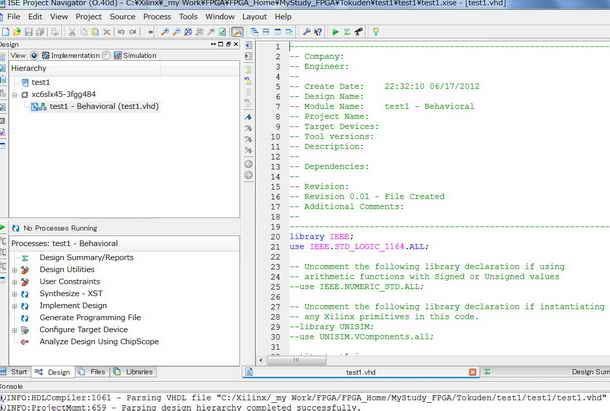

・ (VHDL)ソースファイルのひな形がエディタウィンドウ(仮称)に現れます。

・ひな形をもとに(VHDL)ソースファイルを作成します。

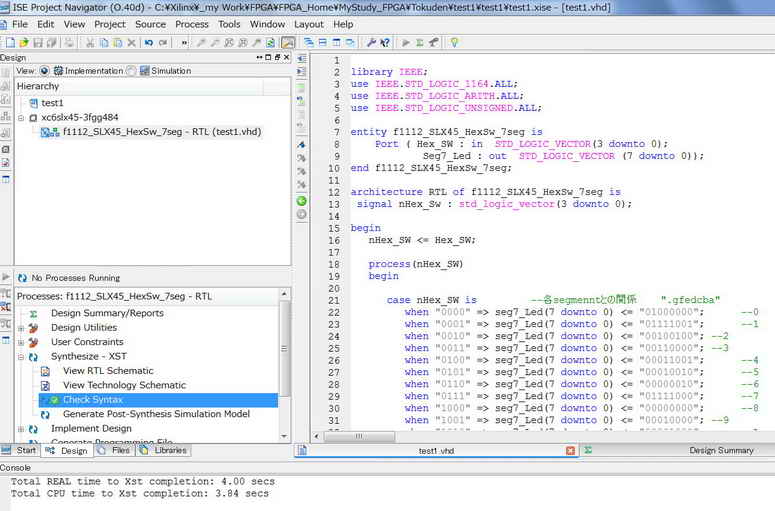

・ ソースファイルにSyntaxエラーがないか プロセスウィンドウのCheck Syntaxでチェックします。 OKであれば Check Sy;ntaxの先頭に緑のチェックが、NGであれば赤のXがあれわれます。

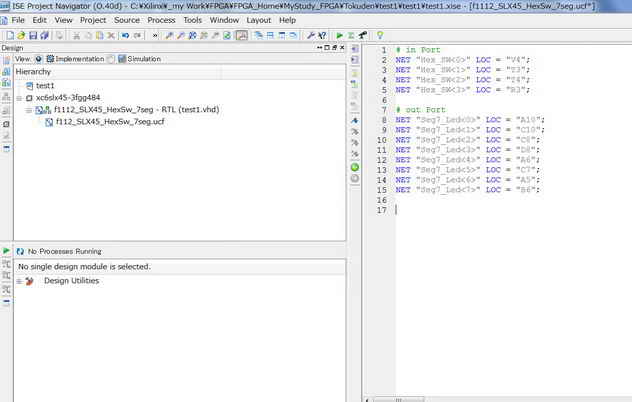

■ ピン番号の指定

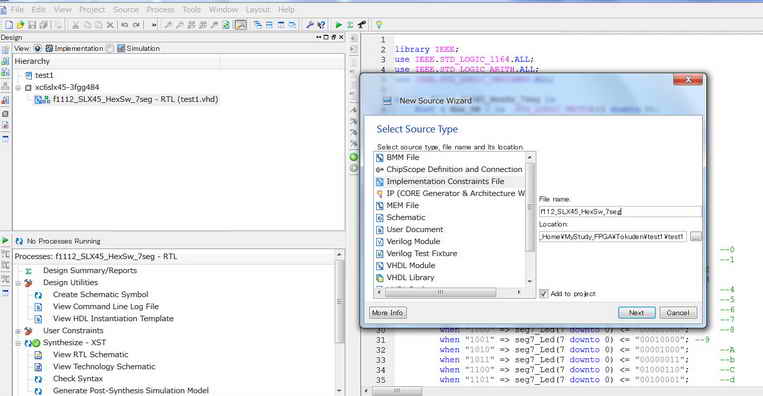

・*.vhdファイルを右クリックして *.ucfファイルを追加します。

なお、グラフィックエディタとして、[User Constraint] → [ Floorplan -PreStynthesis] (CLPDの場合)、I/O

Pin Planing、FloorPlan Area/IO/Logic(Plan Ahead) (FPGAの場合)]などが使用できます。

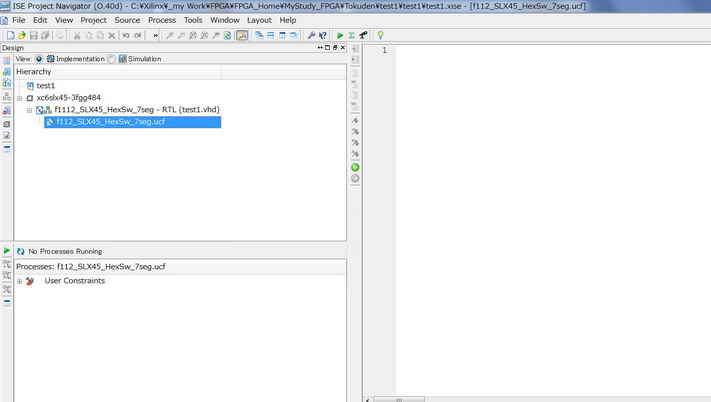

・*.ucfファイルが追加されました。

・*.ucfファイルに 使用するポートとピン番号との相関をコーディングします。

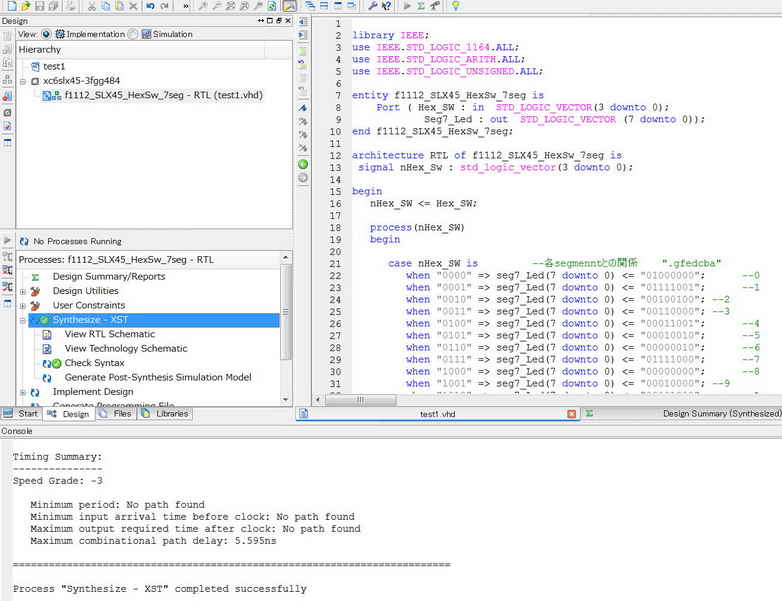

■ 論理合成

・ 次に ソースファイルをプロセスウィンドウの Synthesize-XSTをダブルクリックして 論理合成をおこないます。 正常に終了すると緑のチェックつきます。

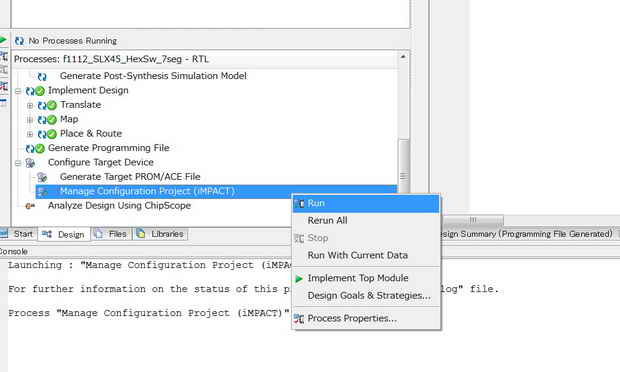

■ 書込みファイル作成

・Manage Configuration Project(iMPACT)を右クリックして ショートカットメニュウを表示させます。 Run

をクリックして、書込みファイル*.JEDECを作成します。

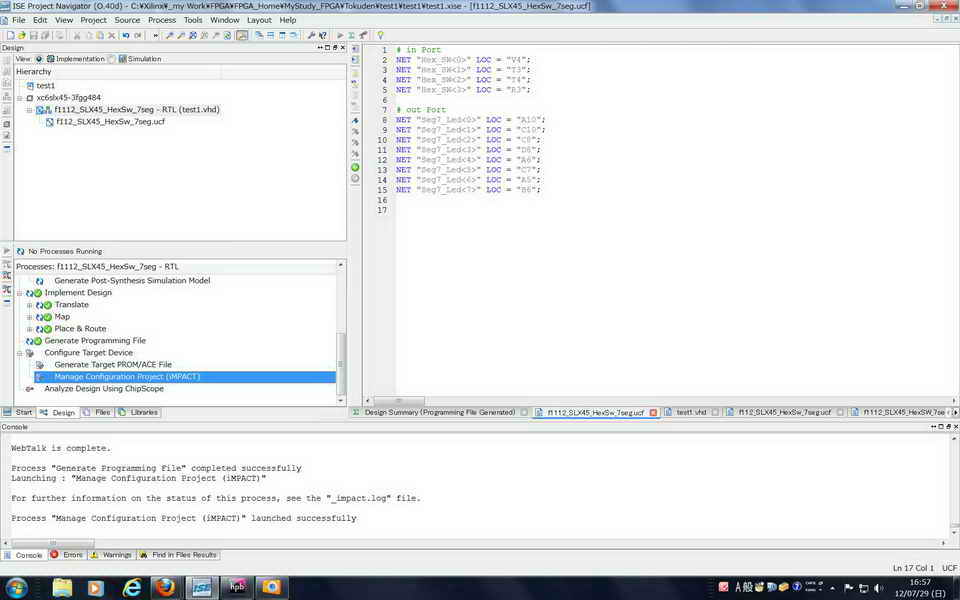

・成功すると Console ウィンドウに …… Project "(iMPACT)" lauched successfullyが表示されます。

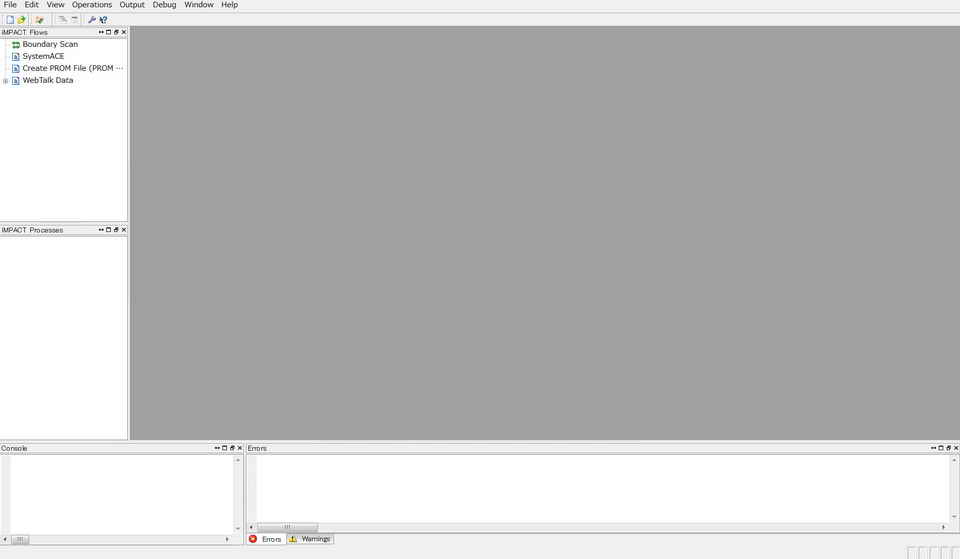

・Manage Configuration Project(iMPACT) をダブルクリックすると書込み画面が立上ります

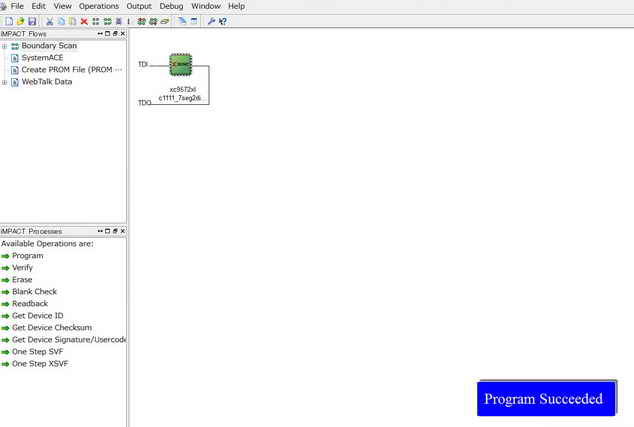

■ デバイスへの書込み

・ターゲットボードとプログラマ(書込み器)を接続します。

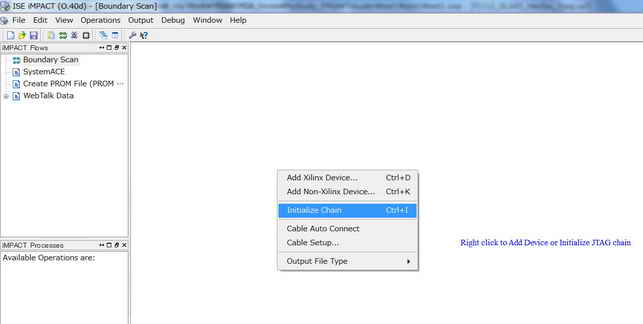

・Boundary Scan をダブルクリックして、中央画面の中で右クリックします。ショートカットメニューがあらわれますのでInitialize

Chainをクリックします。

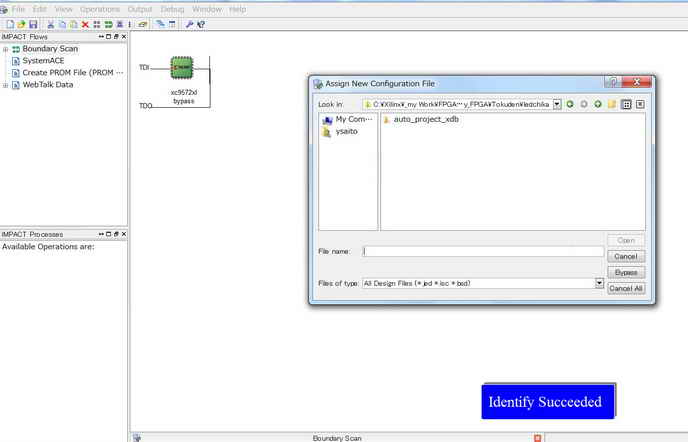

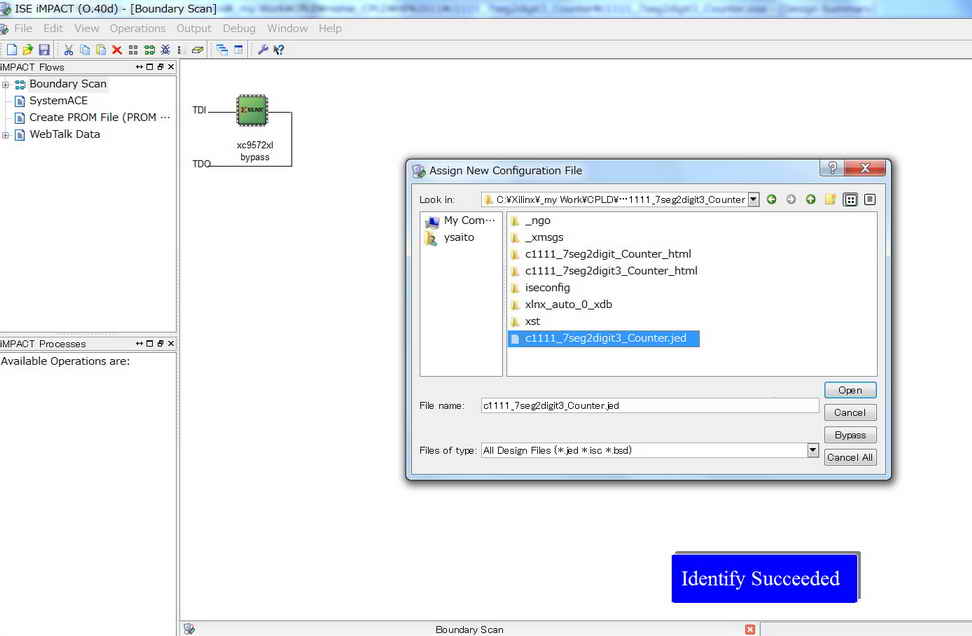

デバイスが見つかると successfullyがあらわれます。

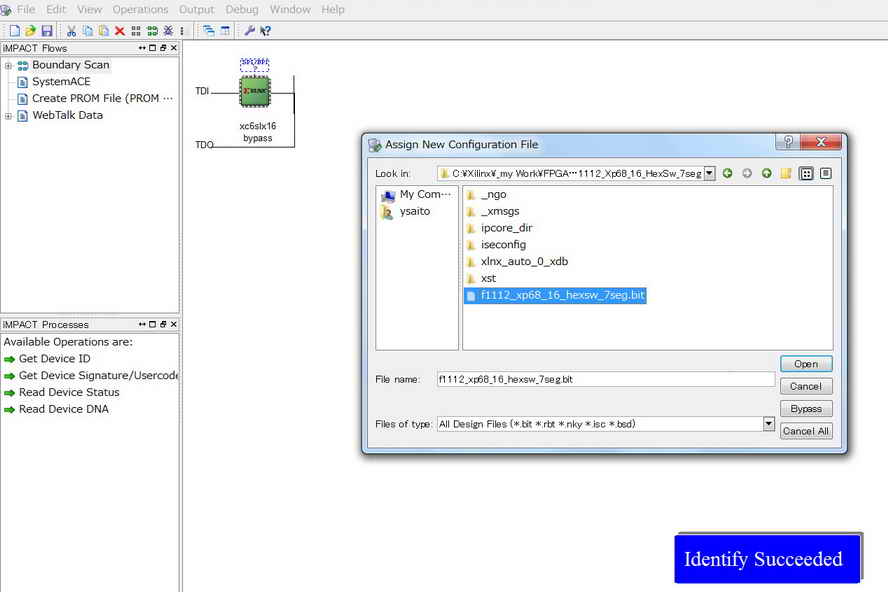

・ 書込みファイル(CPLD: * . jed、 FPGA: * . bit)を選択します。

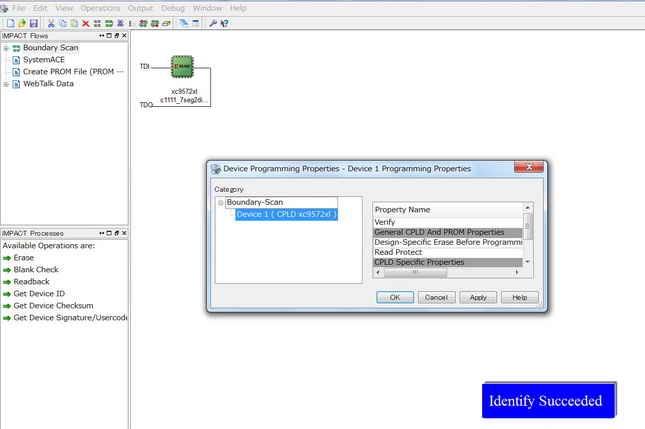

(CPLDの場合)

(FPGAの場合)

・ 確認の画面があらわれますので Okをクリックします。

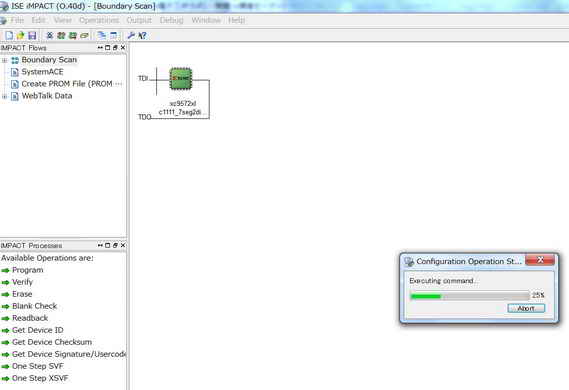

・デバイスの上で右クリックして program により書込みます。

・デバイスへの書込みが開始されます。

・ デバイスへの書き込みが成功しました。