�@�@�@��H�u���b�N ���C�u�����[

���@D�^�t���b�v�t���b�v�i74xx74�����j

�@�@������i�d�l��

�@�@�@�E�@�N���b�N�̗����オ��Ńf�[�^�����b�`���邱��

�@�@�@�E�@�N���A�[�q�A�v���Z�b�g�[�q��L���邱��

�@�@�@�E�@�ėp���W�b�NIC�@74xx74�����̋@�\�E���\�ł��邱�Ƃ���

�@�@�@�@�@�@

�@�@���u���b�N�}��

�@

�@�@������i��H�}���i��H�}��PDF�t�@�C���j

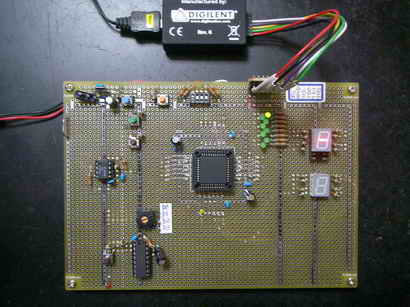

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂��B

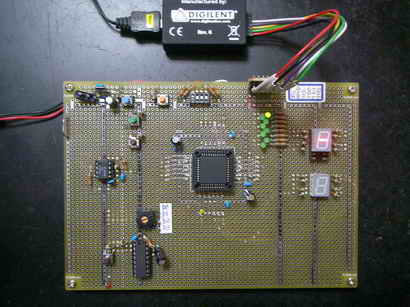

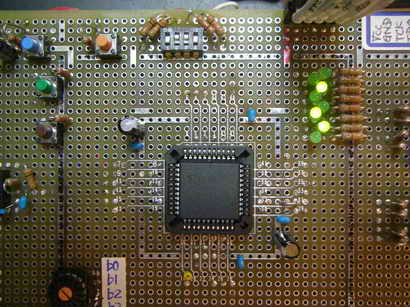

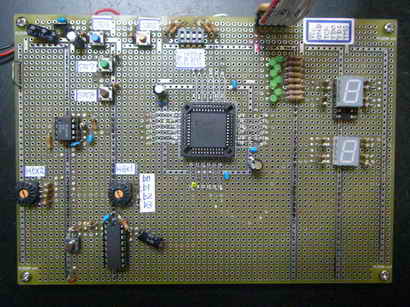

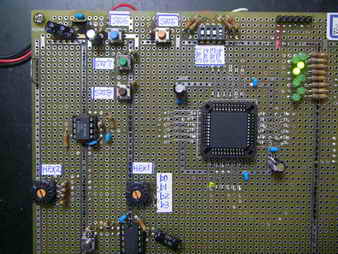

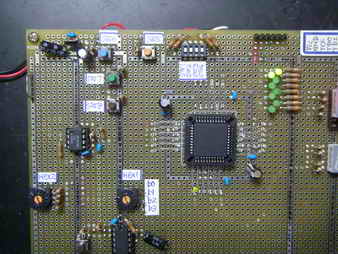

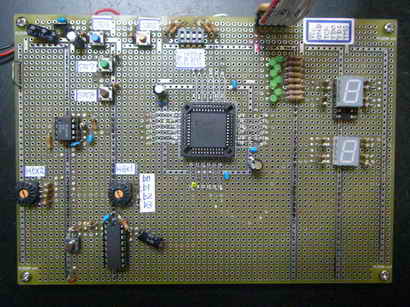

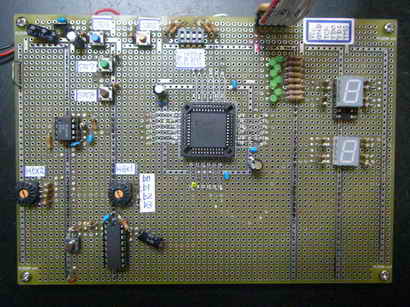

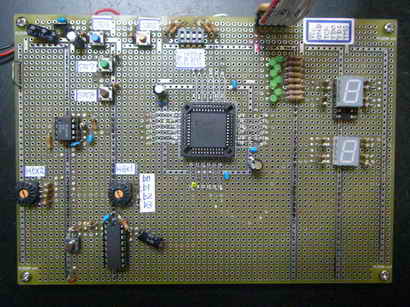

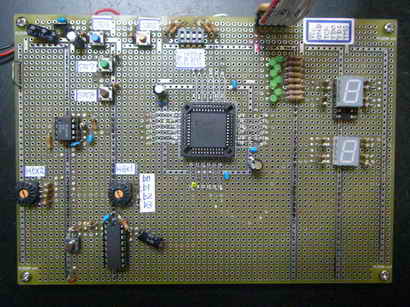

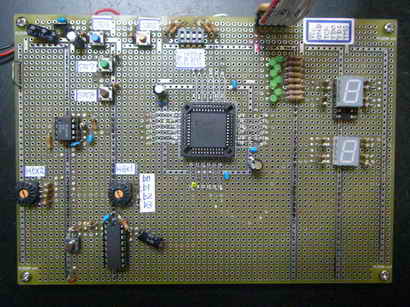

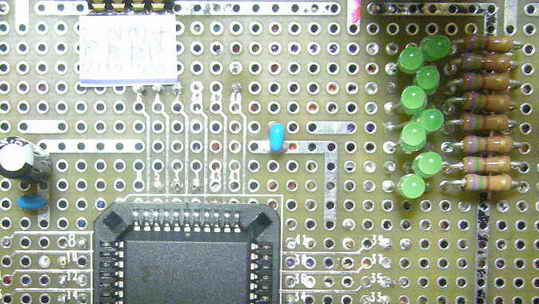

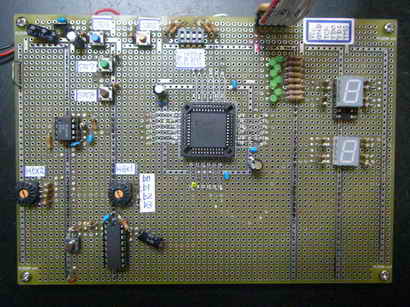

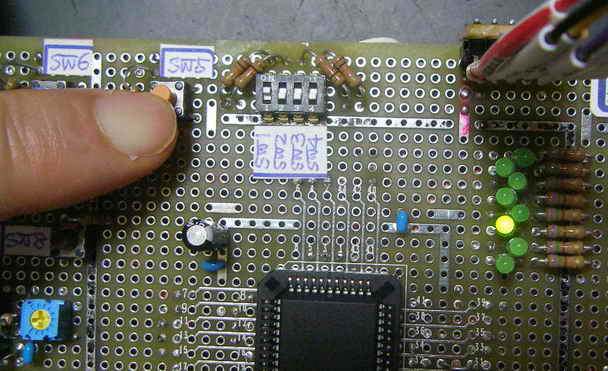

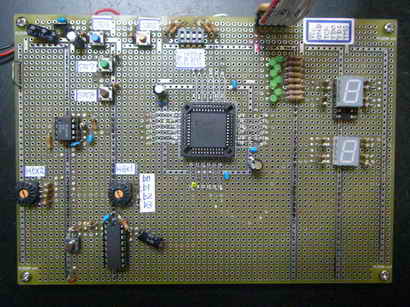

�@������i�O�ρ����L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity c1110_Dtype_FF_full is

Port ( Data : in STD_LOGIC;

CLK : in STD_LOGIC;

CLR : in STD_LOGIC;

PR : in STD_LOGIC;

Q : out STD_LOGIC;

nQ : out STD_LOGIC);

end c1110_Dtype_FF_full;

architecture RTL of c1110_Dtype_FF_full is

begin

process(CLK,CLR,PR)

begin

if(CLR = '0')then --�N���A�̏ꍇ

Q <= '0';

nQ <= '1';

elsif(PR = '0')then --�v���Z�b�g�̏ꍇ

Q <= '1';

nQ <= '0';

elsif(CLK'event and CLK = '1')then --�N���b�N�̗����オ������o�����ꍇ

Q <= Data;

nQ <= not Data;

end if;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "CLK" LOC = "P18" ; NET "CLR" LOC = "P2" ; NET "Data" LOC = "P1" ; NET "nQ" LOC = "P43" ; NET "PR" LOC = "P3" ; NET "Q" LOC = "P44" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

----------------------------------------------------

�����쌋�ʁ�

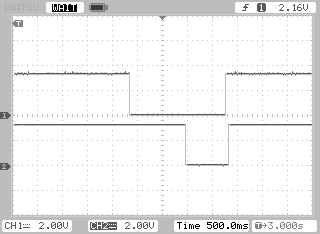

�@�N���b�N�͎蓮�Ž����������A�P����}���`�o�C�u���[�^�Ŕg�`���`����100msec���̃p���X����͂��܂����B

| �@ �t���b�v�t���b�v�̃��[�h�@ |

���쌋�� |

| Q���P NQ=0 |

|

| Q=0 NQ=1 |

|

�@���@�V�Z�O�����g �f�R�[�_

�@������i�d�l��

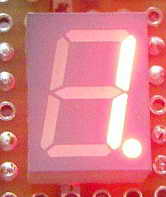

�@�@�EHEX�X�`�b�`����̂S�r�b�g�̃o�C�i�����͂��V�Z�O�����gLED�ɉ��L�̂悤�ɕ\������B�@�@

| �o�C�i�����́@(b(3) b(2) b(1) b(0)) | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| �V�Z�O�����gLED�\�� | �O | �P | �Q | �R | �S | �T | �U | �V | �W | �X | A | �� | C | �� | E | F |

�@�@�E�V�Z�O�����gLED�̃h�b�g�͊O���X�C�b�`����ON/OFF�ł��邱��

�@�@���u���b�N�}��

�@

�@

�@�@������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂��B

������i�O�ρ����L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity c1110_7segment_full is

Port ( Hex_Sw : in STD_LOGIC_VECTOR (3 downto 0);

Dot_Sw : in STD_LOGIC;

seg7_Led : out STD_LOGIC_VECTOR (7 downto 0));

end c1110_7segment_full;

architecture RTL of c1110_7segment_full is

signal nHex_Sw : std_logic_vector(3 downto 0);

begin

nHex_Sw <= not Hex_Sw;

process(Dot_Sw)

begin

if(Dot_Sw = '1')then

case nHex_Sw is --�esegmennt�Ƃ̊W ".gfedcba"

when "0000" => seg7_Led(7 downto 0) <= "01000000"; --0

when "0001" => seg7_Led(7 downto 0) <= "01111001"; --1

when "0010" => seg7_Led(7 downto 0) <= "00100100"; --2

when "0011" => seg7_Led(7 downto 0) <= "00110000"; --3

when "0100" => seg7_Led(7 downto 0) <= "00011001"; --4

when "0101" => seg7_Led(7 downto 0) <= "00010010"; --5

when "0110" => seg7_Led(7 downto 0) <= "00000010"; --6

when "0111" => seg7_Led(7 downto 0) <= "01111000"; --7

when "1000" => seg7_Led(7 downto 0) <= "00000000"; --8

when "1001" => seg7_Led(7 downto 0) <= "00010000"; --9

when "1010" => seg7_Led(7 downto 0) <= "00001000"; --A

when "1011" => seg7_Led(7 downto 0) <= "00000011"; --b

when "1100" => seg7_Led(7 downto 0) <= "01000110"; --C

when "1101" => seg7_Led(7 downto 0) <= "00100001"; --d

when "1110" => seg7_Led(7 downto 0) <= "00000110"; --E

when "1111" => seg7_Led(7 downto 0) <= "00001110"; --F

when others => seg7_Led(7 downto 0) <= "00000000"; --���̑��̏ꍇ

end case;

elsif(Dot_Sw = '0')then

case nHex_Sw is

when "0000" => seg7_Led(7 downto 0) <= "11000000"; --0

when "0001" => seg7_Led(7 downto 0) <= "11111001"; --1

when "0010" => seg7_Led(7 downto 0) <= "10100100"; --2

when "0011" => seg7_Led(7 downto 0) <= "10110000"; --3

when "0100" => seg7_Led(7 downto 0) <= "10011001"; --4

when "0101" => seg7_Led(7 downto 0) <= "10010010"; --5

when "0110" => seg7_Led(7 downto 0) <= "10000010"; --6

when "0111" => seg7_Led(7 downto 0) <= "11111000"; --7

when "1000" => seg7_Led(7 downto 0) <= "10000000"; --8

when "1001" => seg7_Led(7 downto 0) <= "10010000"; --9

when "1010" => seg7_Led(7 downto 0) <= "10001000"; --A

when "1011" => seg7_Led(7 downto 0) <= "10000011"; --b

when "1100" => seg7_Led(7 downto 0) <= "11000110"; --C

when "1101" => seg7_Led(7 downto 0) <= "10100001"; --d

when "1110" => seg7_Led(7 downto 0) <= "10000110"; --E

when "1111" => seg7_Led(7 downto 0) <= "10001110"; --F

when others => seg7_Led(7 downto 0) <="10000110"; --���̑��̏ꍇ

end case;

end if;

end process;

end RTL;

�@��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Dot_Sw" LOC = "P1" ; NET "Hex_Sw<0>" LOC = "P14" ; NET "Hex_Sw<1>" LOC = "P13" ; NET "Hex_Sw<2>" LOC = "P12" ; NET "Hex_Sw<3>" LOC = "P11" ; NET "seg7_Led<0>" LOC = "P24" ; NET "seg7_Led<1>" LOC = "P25" ; NET "seg7_Led<2>" LOC = "P26" ; NET "seg7_Led<3>" LOC = "P28" ; NET "seg7_Led<4>" LOC = "P29" ; NET "seg7_Led<5>" LOC = "P33" ; NET "seg7_Led<6>" LOC = "P34" ; NET "seg7_Led<7>" LOC = "P27" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

----------------------------------------------

�����쌋�ʁ�

| �o�C�i������ | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

| �V�Z�O�����gLED �\�� |

|

|

|

|

|

|

|

|

| �o�C�i������ | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| �V�Z�O�����g �\�� |

|

|

|

|

|

|

|

|

���@�W�r�b�g���b�`(74XX574�A74XX374�����j

�@

�@�@������i�d�l��

�@�E�W�r�b�h�̃p�������f�[�^���@�N���b�N�̗����オ��Ń��b�`�ł��邱�ƁB

�@�E���Z�b�g�M���Ńf�[�^���N���A�ł��邱�ƁB

�@�E�ėp���W�b�NIC�@74XX574�A74XX374�����̐��\�E�@�\��L���邱�ƁB

�@���u���b�N�}��

�@

�@�@������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂��B

������i�O�ρ����L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Latch_8bit is

Port ( data_in : in STD_LOGIC_VECTOR (7 downto 0);

data_out : out STD_LOGIC_VECTOR (7 downto 0);

Clk : in STD_LOGIC;

Reset : in STD_LOGIC);

end Latch_8bit;

architecture RTL of Latch_8bit is

begin

process(Reset,Clk)

begin

if(Reset = '0')then -- ���Z�b�g�̏ꍇ

data_out <= "00000000";

elsif(Clk' event and Clk = '1')then --�N���b�N�������オ�����ꍇ

data_out <= data_in; --���̓f�[�^���o�͂���

end if;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P18" ; NET "data_in<0>" LOC = "P1" ; NET "data_in<1>" LOC = "P2" ; NET "data_in<2>" LOC = "P3" ; NET "data_in<3>" LOC = "P4" ; NET "data_in<4>" LOC = "P14" ; NET "data_in<5>" LOC = "P13" ; NET "data_in<6>" LOC = "P12" ; NET "data_in<7>" LOC = "P11" ; NET "data_out<0>" LOC = "P35" ; NET "data_out<1>" LOC = "P36" ; NET "data_out<2>" LOC = "P37" ; NET "data_out<3>" LOC = "P38" ; NET "data_out<4>" LOC = "P39" ; NET "data_out<5>" LOC = "P40" ; NET "data_out<6>" LOC = "P43" ; NET "data_out<7>" LOC = "P44" ; NET "Reset" LOC = "P6" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

----------------------------------------

�����쌋�ʁ�

�@�蓮�����ɂ��A�P����}���`��100msec�̃N���b�N�p���X�������@���b�`�@�y�у��Z�b�g�����ڎ��m�F���܂����B

���@�Sbit�@BCD�@�Z���N�^

�@������i�d�l��

�@�@�E�Q�̂S�r�b�gBCD�f�[�^�̂����ꂩ��I������B

�@�@�E�I��M���͂S�r�b�g�M���Ƃ��A0000-0111�̏ꍇ�́@HEX SW1�̃f�[�^���@1000-1111�̏ꍇ��HEX SW2��

�@�@�@�f�[�^���o�͂��邱�ƁB

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂��B

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

�@���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity c1111_4bitBCD_Selector is

Port ( In1 : in STD_LOGIC_VECTOR (3 downto 0);

In2 : in STD_LOGIC_VECTOR (3 downto 0);

OutX : out STD_LOGIC_VECTOR (3 downto 0);

Select_Bus : in STD_LOGIC_VECTOR (3 downto 0));

end c1111_4bitBCD_Selector;

architecture RTL of c1111_4bitBCD_Selector is

begin

process(Select_Bus)

begin

case Select_Bus(3 downto 0) is

when "0000" => OutX <= In1;

when "0001" => OutX <= In1;

When "0010" => OutX <= In1;

When "0011" => OutX <= In1;

When "0100" => OutX <= In1;

When "0101" => OutX <= In1;

When "0110" => OutX <= In1;

When "0111" => OutX <= In1;

When others => OutX <= In2;

end case;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "In1<0>" LOC = "P14" ; NET "In1<1>" LOC = "P13" ; NET "In1<2>" LOC = "P12" ; NET "In1<3>" LOC = "P11" ; NET "In2<0>" LOC = "P9" ; NET "In2<1>" LOC = "P8" ; NET "In2<2>" LOC = "P7" ; NET "In2<3>" LOC = "P6" ; NET "OutX<0>" LOC = "P39" ; NET "OutX<1>" LOC = "P40" ; NET "OutX<2>" LOC = "P43" ; NET "OutX<3>" LOC = "P44" ; NET "Select_Bus<0>" LOC = "P1" ; NET "Select_Bus<1>" LOC = "P2" ; NET "Select_Bus<2>" LOC = "P3" ; NET "Select_Bus<3>" LOC = "P4" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

-----------------------------------------------------------------------

�����쌋�ʁ�

| Selector�F�@0000�`0111�@�̏ꍇ | Selector�F�@1000�`1111�̏ꍇ |

|

|

���@�����^�W�r�b�g �A�b�v߃J�E���^

�@������i�d�l��

�@�E�N���b�N�M���̗����オ��ŃJ�E���g�A�b�v���邱�ƁB

�@�E�o�͂͂W�r�b�g�o�C�i���[�o�͂Ƃ���B

�@�E�Q�T�T�̎��͂O�ɖ߂�\������B�ȉ�������J��Ԃ��B

�@�E���Z�b�g�M���ŃJ�E���^�l���O�ɂȂ邱�ƁB

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂��B

�@

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

�@���v���O�����၄

�@��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL; --�Z�p���Z���̌Ăяo��

use IEEE.STD_LOGIC_UNSIGNED.ALL; --�����Ȃ����Z���̌Ăяo��

entity c1111_8bit_Counter is

Port ( Clk : in STD_LOGIC;

Reset : in STD_LOGIC;

Outx : out STD_LOGIC_VECTOR (7 downto 0));

end c1111_8bit_Counter;

architecture RTL of c1111_8bit_Counter is

signal Outy: std_logic_vector(7 downto 0);

signal nReset: std_logic;

begin

nReset <= not Reset; --�ɐ����]

process(nReset,Clk)

begin

if(nReset = '1')then

Outy <= "00000000";

elsif (Clk' event and Clk = '1') then

Outy <= Outy + '1'; --�v�@�@use IEEE.STD_LOGIC_UNSIGNED.ALL; --�����Ȃ����Z���̌Ăяo��

end if;

Outx <= Outy;

end process;

end RTL;

�@��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P18" ; NET "Outx<0>" LOC = "P35" ; NET "Outx<1>" LOC = "P36" ; NET "Outx<2>" LOC = "P37" ; NET "Outx<3>" LOC = "P38" ; NET "Outx<4>" LOC = "P39" ; NET "Outx<5>" LOC = "P40" ; NET "Outx<6>" LOC = "P43" ; NET "Outx<7>" LOC = "P44" ; NET "Reset" LOC = "P6" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

----------------------------------------------------------------

�����쌋�ʁ�

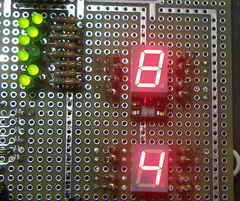

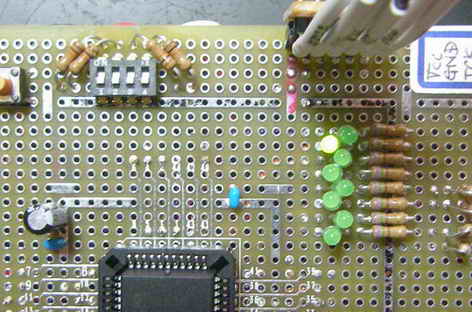

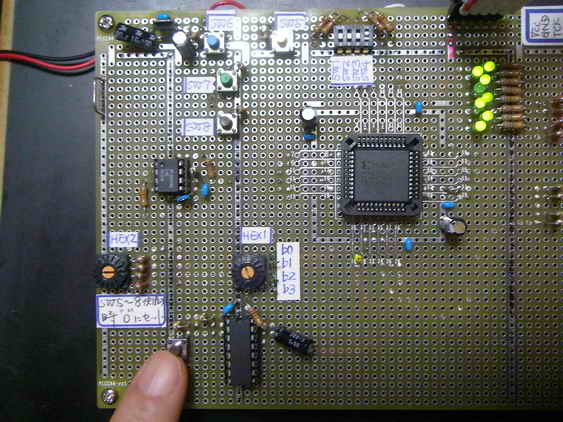

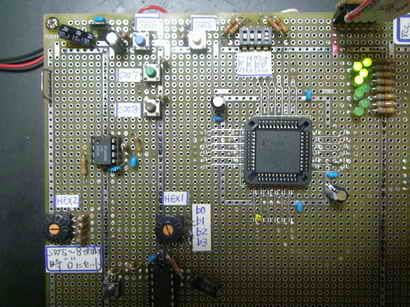

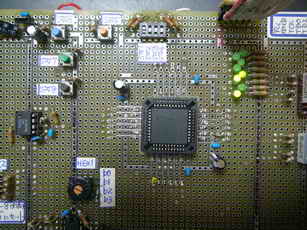

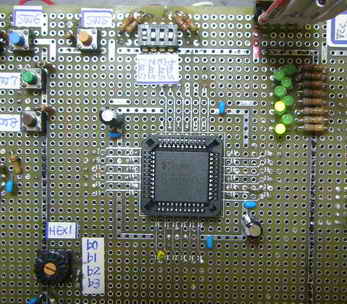

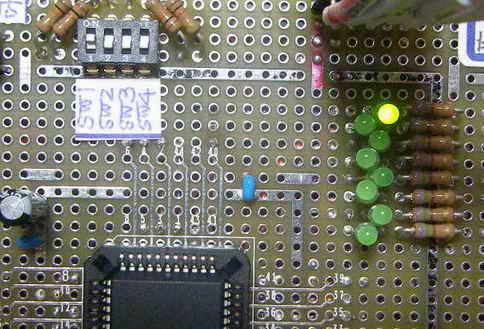

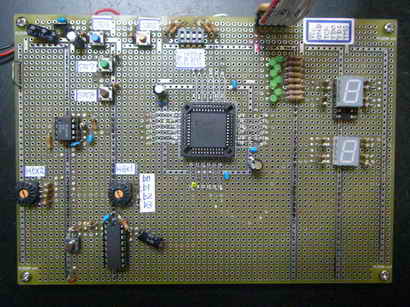

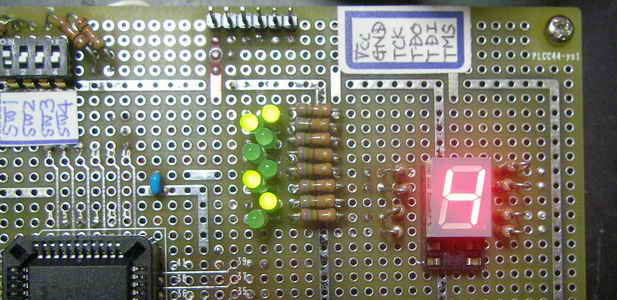

�@�@�蓮��16��A�����{�^���X�C�b�`�����������̎ʐ^�ł��B�@���i4�j��LED�������������Ă��܂��B

���@�W�r�b�g�@�V�t�g���W�X�^�i�V���A��in�@���@�p������out�j�i�V�S�����P�U�S�����j

�@������i�d�l��

�@�E�N���b�N�̗����オ��Ńf�[�^��ǂݍ��ނ��ƁB

�@�E�o�̓f�[�^�̓N���b�N�̗����オ�薈�ɒ����o�͂̂��ƁB�B

�@�E���Z�b�g�ł��邱�ƁB

�@�E74HXX�P�U�S�����̋@�\�E���\��L���邱�ƁB

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂��B

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL; --�Z�p���Z���̌Ăяo��

use IEEE.STD_LOGIC_UNSIGNED.ALL; --�����Ȃ����Z���̌Ăяo��

entity c1111_8bit_ShiftResister_Sin is

Port ( Clk : in STD_LOGIC;

Data_Seri : in STD_LOGIC;

Data_Parax : out STD_LOGIC_VECTOR (7 downto 0);

Reset : in STD_LOGIC);

end c1111_8bit_ShiftResister_Sin;

architecture RTL of c1111_8bit_ShiftResister_Sin is

signal nReset: std_logic;

signal Data_Paray: std_logic_vector(7 downto 0); --������p�o�͐ݒ�

begin

nReset <= not Reset; --�ɐ����]

process(nReset,Clk)

begin

if(nReset = '1')then

Data_Paray <= "00000000"; --���Z�b�g

elsif (Clk' event and Clk = '1')then

Data_Paray <= Data_Paray(6 downto 0) & Data_Seri; --�x�N�^�z��̃X���C�X�@�y��LSB�̌���

end if;

Data_Parax <= Data_Paray;

end process;

end RTL;

��ucf�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P18" ; NET "Data_Parax<0>" LOC = "P35" ; NET "Data_Parax<1>" LOC = "P36" ; NET "Data_Parax<2>" LOC = "P37" ; NET "Data_Parax<3>" LOC = "P38" ; NET "Data_Parax<4>" LOC = "P39" ; NET "Data_Parax<5>" LOC = "P40" ; NET "Data_Parax<6>" LOC = "P43" ; NET "Data_Parax<7>" LOC = "P44" ; NET "Data_Seri" LOC = "P1" ; NET "Reset" LOC = "P6" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

--------------------------------------------

�����쌋�ʁ�

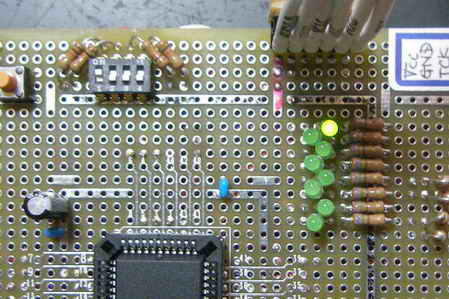

�@�蓮������"00001111"����ʃr�b�g���珇���A4�N���b�N���������̎ʐ^�ł��B

���@�S�r�b�g�@�A�b�_�[�i���Z��j

�@������i�d�l��

�@�E�Q�̂S�r�b�g�f�[�^�����Z���ďo�͂���B

�@

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All; --�Z�p���Z���̌Ăяo��

use Ieee.Std_Logic_Unsigned.All; --�����Ȃ����Z���̌Ăяo��

entity c1111_4bit_Adder is

Port ( Data1 : in STD_LOGIC_VECTOR (3 downto 0);

Data2 : in STD_LOGIC_VECTOR (3 downto 0);

Added_Data : out STD_LOGIC_VECTOR (3 downto 0));

end c1111_4bit_Adder;

architecture RTL of c1111_4bit_Adder is

signal nData1: std_logic_vector(3 downto 0);

signal nData2: std_logic_vector(3 downto 0);

signal Added_Datax: std_logic_vector(3 downto 0);

begin

nData1 <= not Data1; --�ɐ����]

nData2 <= not Data2; --�ɐ����]

process(nData1,nData2)

begin

Added_Datax <= nData1 + nData2; --���Z���Z

Added_Data <= Added_Datax;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Added_Data<0>" LOC = "P35" ; NET "Added_Data<1>" LOC = "P36" ; NET "Added_Data<2>" LOC = "P37" ; NET "Added_Data<3>" LOC = "P38" ; NET "Data1<0>" LOC = "P1" ; NET "Data1<1>" LOC = "P2" ; NET "Data1<2>" LOC = "P3" ; NET "Data1<3>" LOC = "P4" ; NET "Data2<0>" LOC = "P14" ; NET "Data2<1>" LOC = "P13" ; NET "Data2<2>" LOC = "P12" ; NET "Data2<3>" LOC = "P11" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

--------------------------------------------------------

�����쌋�ʁ�

�@�P�@�{�@�P�@���@�Q�@�̉��Z���Z���������̎ʐ^�������܂��B

�@������i�d�l��

�@�E�@�Q�̂S�r�b�g���̓f�[�^���r���ĉ��L�̏o�͂��������ƁB

�@�@�@�@�@Data1�@���@Data2�@�̏ꍇ

�@�@�@�@�@�@Greater = 1

�@�@�@�@�@�@Equal�@=�@0

�@�@ �@�@�@Smaller�@���@0

�@�@�@�A�@Data1�@=�@Data2�@�̏ꍇ

�@�@�@�@�@�@Greater = 0

�@�@�@�@�@�@Equal�@=�@1

�@�@ �@�@�@Smaller�@���@0

�@�@�@�B�@Data1�@���@Data2�@�̏ꍇ

�@�@�@�@�@�@Greater = 0

�@�@�@�@�@�@Equal�@=�@0

�@�@ �@�@ �@Smaller�@���@1

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.Std_logic_arith.All;

use ieee.Std_logic_unsigned.All;

entity c1111_4bit_Comparator is

Port ( Data1 : in STD_LOGIC_VECTOR (3 downto 0);

Data2 : in STD_LOGIC_VECTOR (3 downto 0);

Greater : out STD_LOGIC;

Equal : out STD_LOGIC;

Smaller : out STD_LOGIC);

end c1111_4bit_Comparator;

architecture RTL of c1111_4bit_Comparator is

signal nData1: std_logic_vector(3 downto 0);

signal nData2: std_logic_vector(3 downto 0);

begin

nData1 <= not Data1; --�ɐ����]

nData2 <= not Data2; --�ɐ����]

process(nData1,nData2)

begin

if(nData1 > nData2)then --�@Data1�̕����傫���ꍇ

Greater <= '1';

Equal <= '0';

Smaller <= '0';

elsif(nData1 < nData2)then --Data1�̕����������ꍇ

Greater <= '0';

Equal <= '0';

Smaller <= '1';

else --�ȏ�̏ꍇ�ȊO�̏ꍇ

Greater <= '0';

Equal <= '1';

Smaller <= '0';

end if;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Data1<0>" LOC = "P1" ; NET "Data1<1>" LOC = "P2" ; NET "Data1<2>" LOC = "P3" ; NET "Data1<3>" LOC = "P4" ; NET "Data2<0>" LOC = "P14" ; NET "Data2<1>" LOC = "P13" ; NET "Data2<2>" LOC = "P12" ; NET "Data2<3>" LOC = "P11" ; NET "Equal" LOC = "P36" ; NET "Greater" LOC = "P37" ; NET "Smaller" LOC = "P35" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

--------------------------------------------------------------

�����쌋�ʁ�

�@�ʐ^�́@Data1���P�AData2���P�@�Ńf�[�^���������ꍇ�̂��̂ł��B

���@���U��

�@������i�d�l��

�@�E�O������̎��g���PKH���̋�`�g�N���b�N�����Ƃɔ��U��삷��B

�@�E�����͂Psec�A�o�́f0�f�iLED��ON�j�̎��Ԃ�500msec�Ƃ���B

�@�E���U��̓N���b�N�����͂���邩����A�����ɔ��U���J�肩�������ƁB

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All; --�Z�p���Z���Ăяo��

use Ieee.Std_Logic_Unsigned.All; --�����Ȃ����Z���Ăяo��

entity c1111_Osc is

Port ( Clk : in STD_LOGIC;

Osc_Out : out STD_LOGIC);

end c1111_Osc;

architecture RTL of c1111_Osc is

signal T0_Count: integer range 0 to 1000; --T0_Count�𐮐��ɐݒ�

begin

process(Clk)

begin

if(Clk' event and Clk = '1')then --�N���b�N���o

T0_Count <= T0_Count + 1; --�C���N�������g

if(T0_Count < 500)then --ON���Ԃ̏ꍇ

--ON���ԁF�@1msec�i= 1/1KHz) �~�@500�@=�@500msec

Osc_Out <= '0';

else --OFF���Ԃ̏ꍇ

Osc_Out <= '1';

end if;

if(T0_Count = 1000)then --�����̃J�E���g�ɂȂ����ꍇ

--�����F 1msec(= 1/1KHz)�@�~�@1000�@=�@1000msec�@=�@1sec

T0_Count <= 0;

end if;

end if;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P5" ; NET "Osc_Out" LOC = "P44" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

--------------------------------------------------------------------------

�����쌋�ʁ�

�@LED������1sec�AON���� 500msec�œ_�ł��J��Ԃ����Ƃ��m�F���܂����B

LED�@�F�@ON |

LED�@�F�@OFF�@ |

|

|

���@���͐M���������o/�����o��

�@������i�d�l��

�@�E�X�C�b�`�M����ON/OFF���O���N���b�N�̗����̃^�C�~���O�Ō��o����B

�@�E�o�͂��O���N���b�N�̗����̃^�C�~���O�ł����Ȃ��B

���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity c1111_SyncroSw_Detect is

Port ( Sw_Detect : in STD_LOGIC;

Led : out STD_LOGIC;

Clk : in STD_LOGIC);

end c1111_SyncroSw_Detect;

architecture RTL of c1111_SyncroSw_Detect is

signal preSw_Detect: Std_Logic;

signal Mode: Std_Logic;

signal nSw_Detect: Std_Logic;

begin

nSW_Detect <= not Sw_Detect; --�ɐ����]

process(Clk)

begin

if(Clk' event and Clk = '1')then

if(preSw_Detect = '0' and nSw_Detect = '1')then -- Sw�F�@OFF �� ON ����茟�o�i�@���@�O��̃N���b�N�ɉ�����X�C�b�`�̏�Ԃƍ���̽����̏�Ԃ��r�j

Mode <= '1'; -- SW ON���[�h

end if;

if(nSw_Detect = '0')then

Mode <= '0';

end if;

Led <= not Mode; --Led �_����������

preSW_Detect <= nSW_Detect; --�����_�̃X�C�b�`�̏�Ԃ��L��

end if;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P5" ; NET "Led" LOC = "P37" ; NET "Sw_Detect" LOC = "P6" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

------------------------------------------------------------------

�����쌋�ʁ�

���@�I���f�B���[�@�^�C�}�i�`���^�����O������H�t�j

�@������i�d�l��

�@�E�����{�^���X�C�b�`����͂Ƃ���I���f�B���C�^�C�}�ɂ��LED��_�������邱��

�@�E�X�C�b�`�̌��o�͂PKHz�̃N���b�N�̗����オ��Ɠ������Ă����Ȃ����ƁB

�@�E�����{�^���ɂ́@�Pmsec���ɂP�O�O��A���ŃX�C�b�`��ON�ł��邱�Ƃ��m�F����`���^�����O������H��

�@�@�������邱�ƁB

�@�ELED�̓_���E�������N���b�N�̗����Ɠ������Ă��邱�ƁB

�@�E�����{�^���X�C�b�`��OFF�ɂȂ�����A�N���b�N�̗����Ɠ������Ă��݂₩�ɏ����̂��ƁB

�@���u���b�N�}��

�@

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All; --�Z�p���Z���Ăяo��

use Ieee.Std_Logic_unsigned.All; --�����Ȃ��������Z���Ăяo��

entity c1111_Timer is

Port ( Sw : in STD_LOGIC;

Clk : in STD_LOGIC;

Led : out STD_LOGIC);

end c1111_Timer;

architecture RTL of c1111_Timer is

signal Count: Integer range 0 to 10000; --�I���f�B���[���Ԃ��ő�1000msec�ɐݒ�

signal Mode_Sw: Integer range 0 to 1; --����SW���o

signal N_Chatt: Integer range 0 to 100; -- Max 100msec

signal Sum: Integer range 0 to 100; --�X�C�b�`���P�ɂȂ����̍��v

signal Detect: Integer range 0 to 1; --�����̃X�C�b�`���o

begin

process(Clk)

begin

if(Clk' event and Clk = '1')then --�N���b�N���オ�茟�o

--�`���^�����O�h�~�@�\�t���X�C�b�`���o

if(Sw = '0')then --SW��Ԍ��o

Detect <= 0;

else

Detect <= 1;

end if;

Sum <= Sum + Detect; --�`���^�����O�h�~

N_Chatt <= N_Chatt + 1;

if(N_Chatt >= 100)then --100msec���Ƀ`�F�b�N

if(Sum = 0)then --100�ׂ�0�iSW�FON�j�Ȃ�

Mode_Sw <= 0; --SW: ON

else

Mode_Sw <= 1; --SW: OFF

end if;

N_Chatt <= 0;

Sum <= 0;

end if;

--�I���f�B���[�^�C�}

if(Mode_Sw = 0)then

Count <= Count + 1;

if(Count > 1000)then -- �I���f�B���[���ԁF�@1000msec

Led <= '0'; --LED�_��

Count <= 0;

end if;

else

Count <= 0;

Led <= '1'; --LED����

end if;

end if;

end process;

end RTL;

��ucf�\�[�X�t�@�C����

#PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P5" ; NET "Led" LOC = "P44" ; NET "Sw" LOC = "P6" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

--------------------------------------------------------------

�����쌋�ʁ�

| ��i�FCH1�@�����{�^��SW�M�� ���i�FCH2�@LED�A�m�[�h�d���@�@�@�@�@�@ |

|

�f�W�^���I�V���F��ʁ@DS-5102

���@�V�Z�O�����g�P���P�U�i�o�C�i���J�E���^

�@������i�d�l��

�@�E�V�Z�O�����gLED�@�~�P�@�ɂO�`F�̕\���������Ȃ��B

�@�E�\�����鐔�l�͉��L�Ɏ����悤�ɁA�@�P�ÂC���N���������āAF�܂ł�������܂��O�ɂ��ǂ邱�ƁB

�@�@�@�@�@�O�@���@�P�@���@�Q�@���R�@���@�c�c�@�c�@D�@���@E�@��F�@���@�O�@���@�P�@���@�c�c

�@�E�C���N�������g�͂P�b���ɍs���邱�ƁB

���u���b�N�}��

�@

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

�@

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

���v���O�����၄

��VHDL�\�[�X�t�@�C����

library IEEE; --�ŏ�w�u���b�N

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity c1111_7seg1digit3_Counter is

Port ( Clk : in STD_LOGIC;

Seg7 : out STD_LOGIC_VECTOR (7 downto 0));

end c1111_7seg1digit3_Counter;

architecture RTL of c1111_7seg1digit3_Counter is

Signal Count1: Integer range 0 to 1000;

Signal Count2: Integer range 0 to 15;

component Display is --�R���|�[�l���g�錾

Port ( Seg : out STD_LOGIC_VECTOR (7 downto 0);

Count : Integer range 0 to 15);

end component;

begin

process(Clk)

begin

if(Clk' event and Clk = '1')then --1msec��

Count1 <= Count1 + 1;

if(Count1 >= 1000)then --1sec��

Count1 <= 0;

Count2 <= Count2 +1; --0�`1�T�̌J��Ԃ�

if(Count2 >= 16)then

Count2 <= 0;

end if;

end if;

end if;

end process;

U1: Display port map(Seg7,Count2);

end RTL;

--------------------------------------------------------------------------------

library IEEE; --���ʑw�u���b�N

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display is --�V�Z�O�����gLED�\�����C�u����

Port( Seg : out STD_LOGIC_VECTOR (7 downto 0);

Count : Integer range 0 to 15);

end Display;

architecture RTL of Display is

begin

process(Count) --�V�Z�O�����gLED�@16�i�\��

begin

case(Count) is

when 0 => Seg <= "11000000"; --0

when 1 => Seg <= "10100100"; --2

when 3 => Seg <= "10110000"; --3

when 4 => Seg <= "10011001"; --4

when 5 => Seg <= "10010010"; --5

when 6 => Seg <= "10000010"; --6

when 7 => Seg <= "11111000"; --7

when 8 => Seg <= "10000000"; --8

when 9 => Seg <= "10010000"; --9

when 10 => Seg <= "10001000"; --A

when 11 => Seg <= "10000011"; --b

when 12 => Seg <= "11000110"; --C

when 13 => Seg <= "10100001"; --d

when 14 => Seg <= "10000110"; --E

when 15 => Seg <= "10001110"; --F

when others => Seg <="10000110"; --���̑��̏ꍇ

end case;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P5" ; NET "Seg7<0>" LOC = "P35" ; NET "Seg7<1>" LOC = "P36" ; NET "Seg7<2>" LOC = "P37" ; NET "Seg7<3>" LOC = "P39" ; NET "Seg7<4>" LOC = "P40" ; NET "Seg7<5>" LOC = "P43" ; NET "Seg7<6>" LOC = "P44" ; NET "Seg7<7>" LOC = "P38" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE

----------------------------------------------------

�����쌋�ʁ�

�@�Psec���ɃJ�E���g���ߒ��ŁA�S��\�������Ƃ���ł��B

���@�V�Z�O�����g�~�Q���@�@10�i�J�E���^

�@������i�d�l��

�@�E�V�Z�O�����gLED�@�~�Q�ɂO�`�X�X�̕\���������Ȃ��B

�@�E�\�����鐔�l�͉��L�Ɏ����悤�ɁA�@�P�ÂC���N���������āA�X�X�܂ł�������܂��O�ɂ��ǂ邱�ƁB

�@�@�@�@�@�O�@���@�P�@���@�Q�@���R�@���@�c�c�@�c�@�X�V�@���@�X�W�@���X�X�@���@�O�@���@�P�@���@�c�c

�@�E�C���N�������g�͂P�b���ɍs���邱�ƁB

�@�E���͂Ƃ��Ă�1KH���̃J�E���^���������邱�ƁB

�@���u���b�N�}��

������i��H�}���i��H�}��PDF�t�@�C���j

�@�ȉ��ɁAXC9572XL���g�����ꍇ��������܂�

������i�O�ρ�

�@�@�@���L�̎ʐ^�ɂ͏�L��H�}�ɂ͂Ȃ��A�܂��{�e�[�}�ƊW�̂Ȃ����i�����X�ʂ��Ă��܂�

�@���v���O�����၄

library IEEE; --�ŏ�w�u���b�N

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity c1111_7seg2digit3_Counter is

Port ( Clk : in STD_LOGIC;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0);

seg7_1 : out Std_Logic_Vector (7 downto 0));

end c1111_7seg2digit3_Counter;

architecture RTL of c1111_7seg2digit3_Counter is

Signal Count1: Integer range 0 to 1000;

Signal Count2: Integer range 0 to 9;

Signal Count3: Integer range 0 to 9;

component Display0 is --�R���|�[�l���g�錾

Port ( Count2 : in Integer range 0 to 10;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0));

end component;

component Display1 is --�R���|�[�l���g�錾

Port ( Count3 : in Integer range 0 to 10;

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end component;

begin

process(Clk)

begin

if(Clk' event and Clk = '1')then --1msec��

Count1 <= Count1 + 1;

if(Count1 >= 1000)then --1sec��

Count1 <= 0;

Count2 <= Count2 +1; --0�`1�T�̌J��Ԃ�

if(Count2 >= 9)then

Count2 <= 0;

Count3 <= Count3 + 1;

if(Count3 >= 9)then

Count3 <= 0;

end if;

end if;

end if;

end if;

end process;

U1: Display0 port map(Count2,Seg7_0);

U2: Display1 port map(Count3,Seg7_1);

end RTL;

----------------------------------------------------------------------

library IEEE; --���ʑw�u���b�N

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display1 is --�V�Z�O�����gLED�\�����C�u����

Port ( Count3 : in Integer range 0 to 10;

Seg7_1 : out STD_LOGIC_VECTOR (7 downto 0));

end Display1;

architecture RTL of Display1 is

begin

process(Count3) --�V�Z�O�����gLED�@16�i�\��

begin

case(Count3) is

when 0 => Seg7_1 <= "11000000"; --0

when 1 => Seg7_1 <= "11111001"; --1

when 2 => Seg7_1 <= "10100100"; --2

when 3 => Seg7_1 <= "10110000"; --3

when 4 => Seg7_1 <= "10011001"; --4

when 5 => Seg7_1 <= "10010010"; --5

when 6 => Seg7_1 <= "10000010"; --6

when 7 => Seg7_1<= "11111000"; --7

when 8 => Seg7_1 <= "10000000"; --8

when 9 => Seg7_1 <= "10010000"; --9

when 10 => Seg7_1 <= "10001000"; --A

when others => Seg7_1 <="10000110"; --���̑��̏ꍇ

end case;

end process;

end RTL;

--------------------------------------------------------------------------

library IEEE; --���ʑw�u���b�N

use IEEE.STD_LOGIC_1164.ALL;

use Ieee.Std_Logic_Arith.All;

use Ieee.Std_Logic_Unsigned.All;

entity Display0 is --�V�Z�O�����gLED�\�����C�u����

Port ( Count2 : in Integer range 0 to 10;

Seg7_0 : out STD_LOGIC_VECTOR (7 downto 0));

end Display0;

architecture RTL of Display0 is

begin

process(Count2) --�V�Z�O�����gLED�@16�i�\��

begin

case(Count2) is

when 0 => Seg7_0 <= "11000000"; --0

when 1 => Seg7_0 <= "11111001"; --1

when 2 => Seg7_0 <= "10100100"; --2

when 3 => Seg7_0 <= "10110000"; --3

when 4 => Seg7_0 <= "10011001"; --4

when 5 => Seg7_0 <= "10010010"; --5

when 6 => Seg7_0 <= "10000010"; --6

when 7 => Seg7_0 <= "11111000"; --7

when 8 => Seg7_0 <= "10000000"; --8

when 9 => Seg7_0 <= "10010000"; --9

when 10 => Seg7_0 <= "10001000"; --A

when others => Seg7_0 <="10000110"; --���̑��̏ꍇ

end case;

end process;

end RTL;

��ucf�\�[�X�t�@�C���� #PACE: Start of Constraints generated by PACE #PACE: Start of PACE I/O Pin Assignments NET "Clk" LOC = "P5" ; NET "Seg7_0<0>" LOC = "P35" ; NET "Seg7_0<1>" LOC = "P36" ; NET "Seg7_0<2>" LOC = "P37" ; NET "Seg7_0<3>" LOC = "P39" ; NET "Seg7_0<4>" LOC = "P40" ; NET "Seg7_0<5>" LOC = "P43" ; NET "Seg7_0<6>" LOC = "P44" ; NET "Seg7_0<7>" LOC = "P38" ; NET "seg7_1<0>" LOC = "P24" ; NET "seg7_1<1>" LOC = "P25" ; NET "seg7_1<2>" LOC = "P26" ; NET "seg7_1<3>" LOC = "P28" ; NET "seg7_1<4>" LOC = "P29" ; NET "seg7_1<5>" LOC = "P33" ; NET "seg7_1<6>" LOC = "P34" ; NET "seg7_1<7>" LOC = "P27" ; #PACE: Start of PACE Area Constraints #PACE: Start of PACE Prohibit Constraints #PACE: End of Constraints generated by PACE ------------------------------------------------------------------------------------------

-----------------------------------------------------------------------------------------

�����쌋�ʁ�

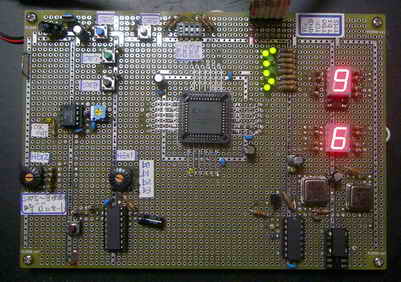

�@�J�E���g��48�̎��̎ʐ^�ł��B�@��i�̉t����1���ځA���i�̉t�����Q���ڂ̃J�E���^����\�����Ă��܂��B